#### Checking Modular Refinements of Bluespec

Nirav Dave<sup>1</sup>, Michael Katelman<sup>2</sup> Massachusetts Institute of Technology<sup>1</sup> University of Illinois at Urbana-Champaign<sup>2</sup>

# Frequently BSV designers refine their designs

# Refinement: Split lookup and modify

```

Mem

FIFO#(int) tempQ <- mkFIFO;</pre>

rule mapReq(i < 100);

i <= i + 1;

tempQ.enq(mem.read(i));

rule mapResp(True);

count \leq count +

F

f(tempQ.first());

tempQ.deq();

+1

count

Pipelined! Better

hardware, but is it

correct?

```

June 3, 2008

### Correctness depends on context i[0], c[0] i[1], c[1] i[2], c[2] ...

New design can observe partially updated state. Rest of system Can't count on i and count to be in sync

• If we were given the whole design can we say if this is okay?

#### Can a tool solve this?

At least for a reasonable class of refinements

- Convert BSV design to TRS\*

- Translate BSV rules in to pure functions

- Use functions to form queries to an bitvector SMT solver

Dealt with this before

# First a bit more about the language

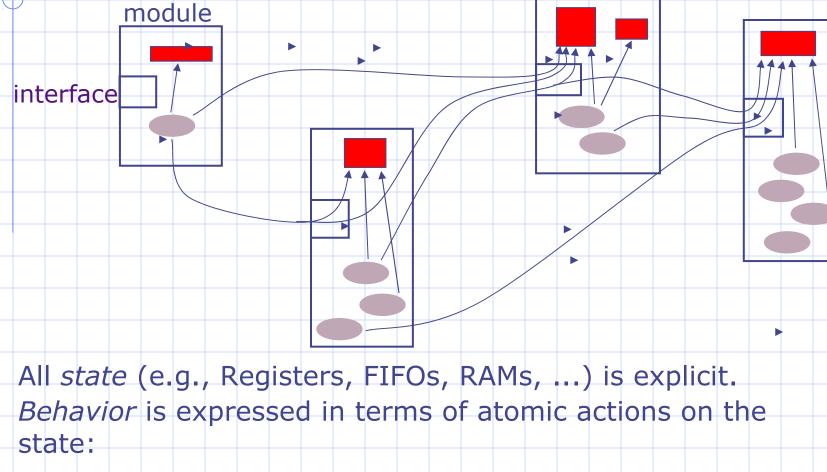

## Bluespec: State and Rules organized into *modules*

#### Rule: guard $\rightarrow$ action

Rules can manipulate state in other modules only via their June 3, imperfaces.

L02-7

#### Rule: As a State Transformer

A rule may be decomposed into two parts  $\pi(s)$  and  $\delta(s)$  such that

$s_{ret} = if \pi(s)$  then  $\delta(s)$  else s

$\pi(s)$  is the guard (predicate)

$\delta(s)$  is the "state transformation" function, i.e., computes the next-state values from the current state values

June 3, 2008

#### Execution model

Repeatedly:

Highly non

Select a rule to execute

deterministic

Compute the state updates

Image: Compute the state updates

Make the state updates

Image: Compute the state updates

Compilation involves deciding how we select rules

- Multiple rules in a cycle

- Tradeoff between parallelism and cycle-level depth

- A lot of flexibility in choice

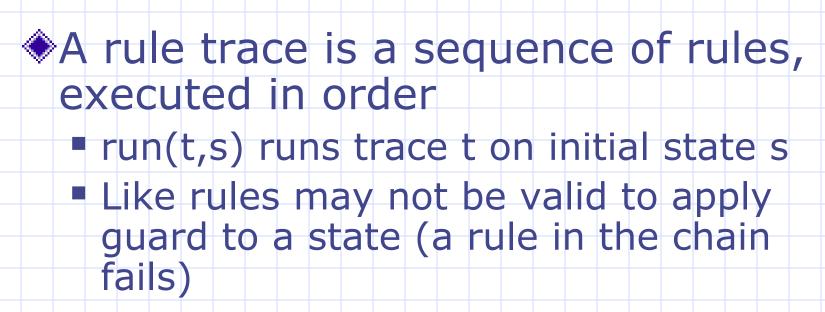

# Rule Traces Rules takes us from State to State

$S \xrightarrow{r1} S' \xrightarrow{r2} S''$

[r1,r2]

June 3, 2008

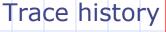

#### The Query

Completeness: Every rule trace in the Spec has a corresponding trace in the Implementation

Soundness: Every rule trace in the implementation has a corresponding trace in the Spec Hard to represent

Infinite traces

What is equality here?

race

rulợ∕

rul

S

́хе

June 3, 2008

#### Handling Infinite Traces

- There are an infinite # of traces

Can we just handle a finite set of finite traces?

- If we have a prefix of a trace, we can reduce the problem to solving it for the tail

If [A,B,C] is fine, then [A,B,C,D,E] reduces to

- If we have a prefix cover for all possible traces of sufficient size, we can always make progress

[D,E]

#### Handling Infinite Traces

Still may need infinite prefix traces

May never reach a comparable state

Show prefix is equivalent to a "safe" trace + a smaller prefix

If [A,B] is safe, and we can show [A,C,D] is the same as [A,B,E], we reduce to [E].

Can get away with considering finite traces

#### Algorithm to find prefix cover

Start with T = traces of length 1

Repeatedly:

- Remove smallest t from T

- Check if we always represent t using safe traces (had a matching point to a spec trace)

- If not add extend t with all possible 1 rule prefix and add to T

- Bail after some size N

- Remaining traces are interesting to designers

#### Trace equality

#### Method Calls to State

input

# All visible history stored in trace Just look at history for equivalence Need to consider all input systems

June 3, 2008

#### **Relating States**

June 3, 2008

#### More simplification

Only consider systems where break one rule into two

Rules in Spec: r12,r3,r4,r5, ...

Rules in Impl: r1, r2, r3', r4', r5',...

\*r12 should correspond to {r1,r2}

Makes completeness easy to prove

#### Queries

Each question takes the form:

$\forall i \in I, s \in S(i).$  is Spec State(s)  $\Rightarrow$

$$\operatorname{run}(t,s) \in \{\operatorname{run}(t',s) \mid t \in T\}$$

- I is the set of possible input

- t is trace we're considering

- T is the set of "safe" traces we want to check against

#### This is easy to cast in SAT

# Reducing the number of Queries

We can find impossible rule traces:

- Many rules cannot fire twice concurrently (FIFOs fill up)

- e.g. [req,req,req]) is impossible

Many rule sequences are equivalent:

- e.g. Rules don't touch same state

- Do not have to check traces T1+[A,B]+T2 since we'll check T1+[B,A]+T21

#### **Current Status**

Simple simple programs : 4 rules

Correct design: 10 seconds (N = 7)

Added an error: 2 seconds (N = 4)

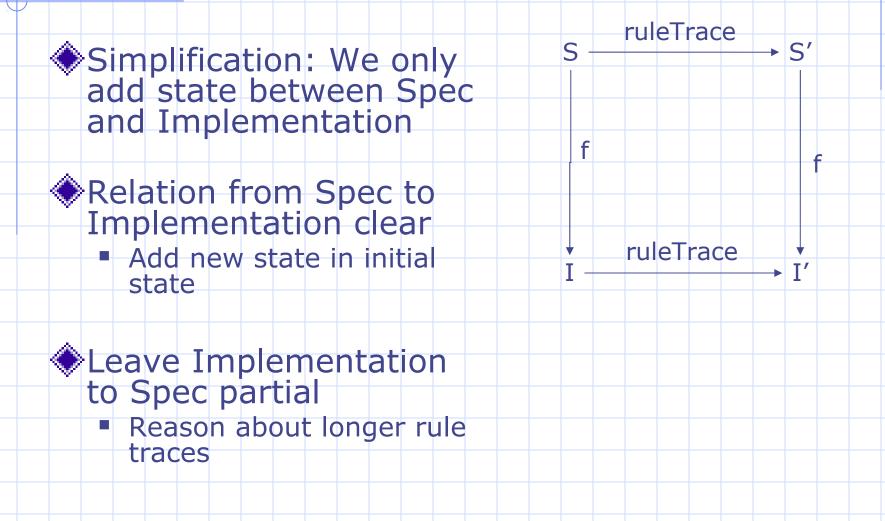

6 stage SMIPS pipeline

- refine to 7 stage (N = 14)

- Many Days of compute

#### Improvements

Trace verification is ridiculously parallel

Parallel execution

Currently, we Represent state as a bitvector

- Does not scale (especially Memories)

- Should move to uninterpreted functions/arrays

Call SMT via file system (write file)

- Significant overhead (>50%)

- Direct interfacing significantly cheaper

#### Summary

Can answer interesting questions about traces in BSV systems

Initial implementation seems pretty reasonable

Efficiency improvements needed to be practical

#### The End

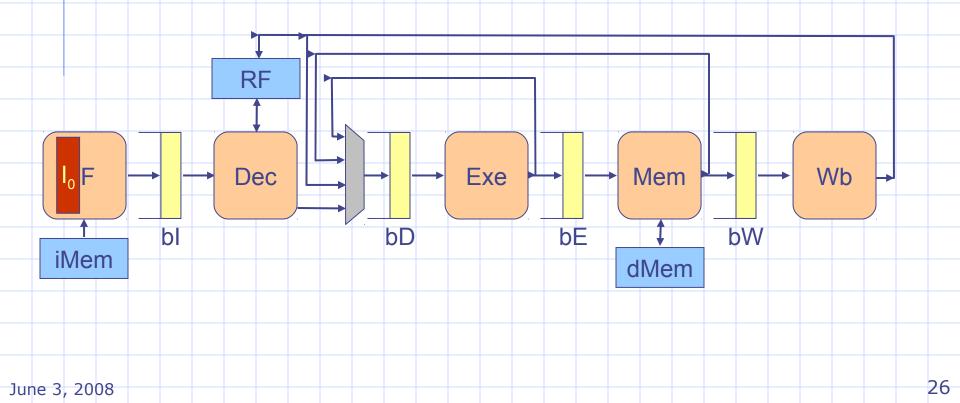

#### Scheduling Flexibility

What order do we want?

Wb < Mem < Exe < Dec < IF

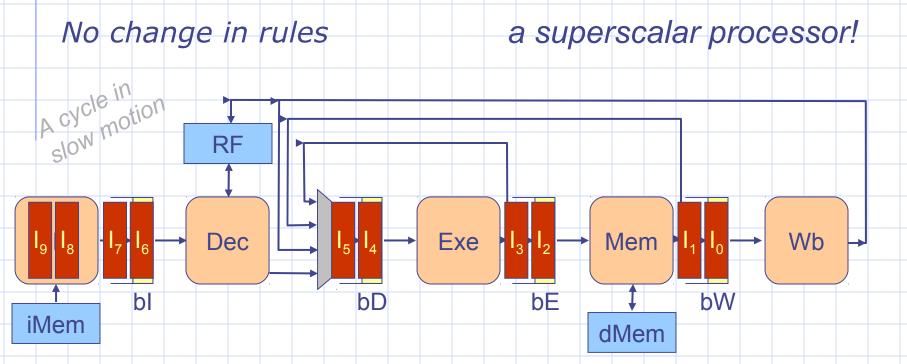

#### Scheduling Flexibility

What if flip the order?

#### Scheduling Flexibility

What happens if the user specifies:

Wb < Wb < Mem < Mem < Exe < Exe < Dec < Dec < IF < IF

Executing 2 instructions per cycle requires more resources but is functionally equivalent to the original design

June 3, 2008

#### **Checking Completeness**

### Given our constraints this should hold

####

### Forall r in {r3,rN}. forall s. isSpec(s) => run(r,s) = run(r',s)

#### **Checking Soundness**

This takes a bit more work as:

We don't really know what traces to compare against. R1,r3?

Can hazard some guesses (permutations? Elisions?)

Some implementation traces do not end in a state the spec can reach:

Extend the sequence and try again

#### Real Question: How much work is this?

What do we have?

BSV Parser (from BSV-SW Compiler)

SMT solver w/ focus on bitvectors

First step - verify scheduling properties

BSV ATS -> Lambda Calculus -> SMT

2 weeks of time

Okay. Maybe we this won't be so bad

So what exactly does it mean to show things are correct?

#### **Bluespec Specification**

Bluespec designs are closer to specifications

- Schedule makes it an implementation

- Guaranteed safe

Spec and Implementation in the same language

Designers mostly do spec. refinement

# What sort of questions can we ask of our solver?

• Convert rule R into  $\pi_R$  and  $\delta_R$ • Use this to ask questions about rule traces:

• [A, B] = [B,A]

• forall s.  $\pi_A(s) \otimes \pi_B(\delta_A(s)) = >$   $\pi_B(s) \otimes \pi_A(\delta_B(s)) \otimes A_A(\delta_B(s)) = \delta_B(\delta_A(s))$

#### Bluespec - Origins

Started from work modeling Cache coherence engines and processors in a Term Rewriting System (TRS) for verification [Stoy, Shen, Arvind]

Precise enough to compile into hardware

- TRAC compiler [Hoe]

- Bluespec Compiler [Augustsson]

# How do we get designers to formally verify?

Reason in the design language Inputs and Results have to be natural Low burden Cannot ask for complex properties Simple predicates / statements Fast feedback Useful in testing

Correctness depends on the context

We've broken the atomicity invariant

i and count are no longer in sync

rule safeRead(i==100 &&

tempQ.first);

if (p(count))

if (p(count))

\$display(i, count);

0kay

Can we verify such changes are safe?

35

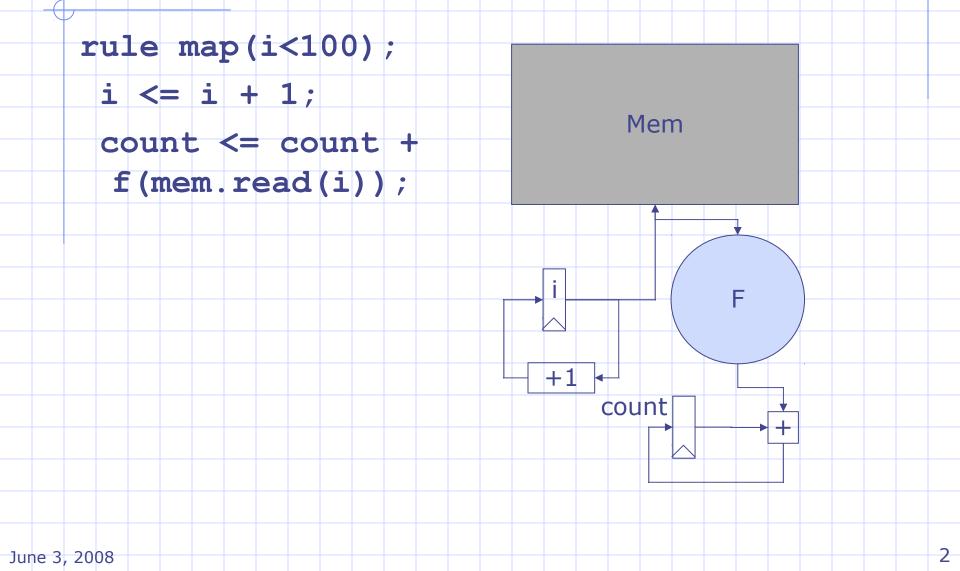

#### Example: modifying memory

Mem mem <<- mkMemory; Reg#(int) i <- mkReg(0); Reg#(int) count <- mkReg(0);</pre>

rule map(i<100);</pre>

i <= i + 1;

count <= count + f(mem.read(i));</pre>

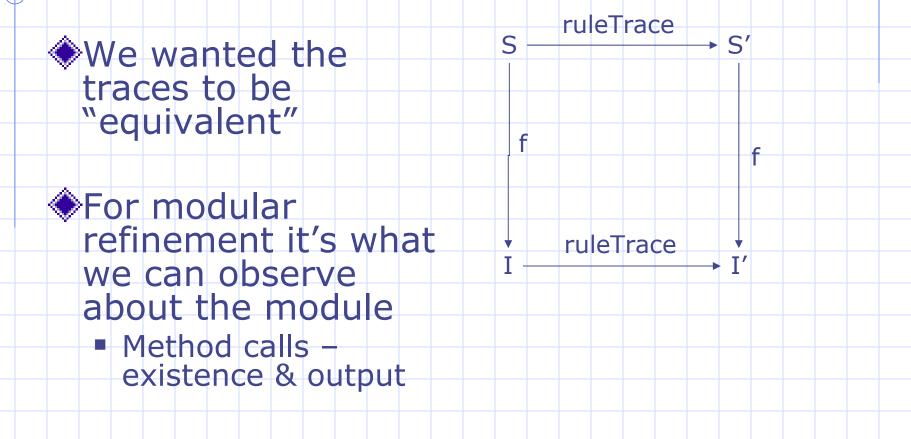

# What does it mean for two modules to be equivalent?

#### Bisimularity:

Every rule trace in A has a corresponding rule trace in B which has the same "observable" effects and vice versa

#### Observations – Method calls

Existence + output value

#### Split lookup and modify

```

Memmem<-</th>mkMem;Reg#(int)i<-</td>mkReg(0);Reg#(int)count<-</td>mkReg(0);FIFO#(int)tempQ<-</td>mkFIFO;

```

```

Rule mapReq(i < 100);

i <= i + 1;

tempQ.enq(mem.read(i));

```

```

rule mapResp(True);

count <= count + f(tempQ.first());

tempQ.deq();

```

#### But!

Now possible to see count and i outof-sync

### We also have the following rule in the system:

rule checkRunningTotal(True);

- if (p(count))

- \$display(i, count);

What refinement do we want to see?

- Pic: One rule cloud to two then three

- Splitting is key.

- Merging also.

- Microsteps.

#### Asking Questions of BSV

Grab compiler dump after static evaluation

TRS of bitvectors and Actions

Convert rules into functions:

- π(s) :: State -> Bool

- δ(s) :: State -> State

Use this to form SAT queries about rule execution traces

*i.e.* Does A followed by B behave like B followed by A?

#### Example:

Reg#(int) x < - mkReg(0); $\operatorname{Reg}$ #(int) y <- mkReg(0); rule swap(x!=0 & & x < y);  $\mathbf{x} \leq \mathbf{y} - \mathbf{x}; \mathbf{y} \leq \mathbf{x};$ endrule method req(nx,ny) when (x==0); $x \leq nx; y \leq ny;$ endmethod method result when (x==0); return y; endmethod

Rl swap guard(s0) =reg\$Rd(getX(s0))!=0 && reg\$Rd(getX(s0))<reg\$Rd(getY(s0))</pre> Rl swap body (s0) = letxv=reg\$Rd(getX(s)) yv=req\$Rd(getY(s)) s1=updX(s0,reg Wr(yv-xv,getX(s0))s2=updY(s1, reg\$Wr(xv,getY(s1))) in s2meth req guard(s0) =regRd(getX(s0)) == 0 meth req body (nx, ny, s0) = let s1=updX(s0,reg Wr(yv-xv,getX(s0))s2=updY(s1, reg Wr(xv, getY(s1)))in s2

#### **Designing Bluespec**

Language aimed at rapid design

Emphasis on refinement

A lot of work

Large designs:

H.264

AirBlue – WiFi baseband